## OPEN. FOR BUSINESS.

## NEW WORKLOADS AND THE EVOLVING NETWORK

Uri Cummings Connectivity Group Chief Technical Officer, Data Center Group Intel Corporation

uri.cummings@intel.com

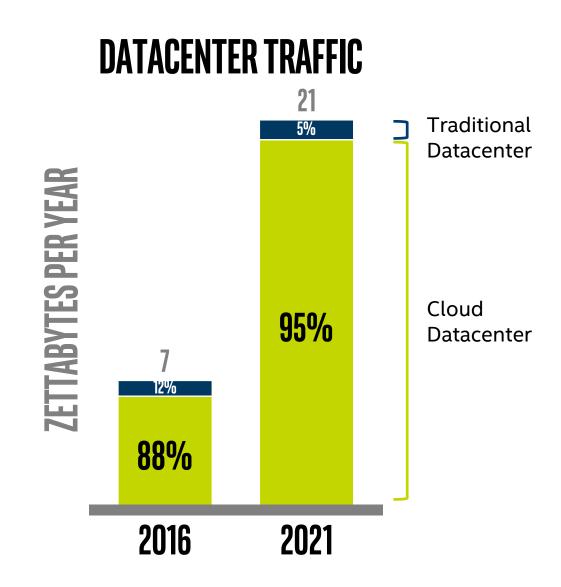

By 2021, 95% of all data center traffic will be based in the cloud.

## Data center network inflections

#### Critical workloads redefine the network

Cloud Scale: the big get bigger

#### Pervasive offloads Distributed intelligence

## Emerging workloads redefining the network Networks reconfigured for east-west, jitter reduction, and accelerators

#### TRADITIONAL NETWORKS AND DATACENTER FABRICS

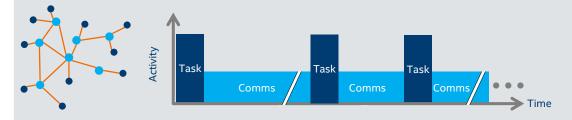

**Network:** Flexibly-connected topology that enables endpoints to share data (e.g., arbitrary non-cyclic topologies)

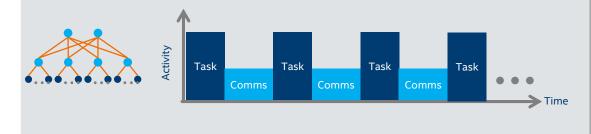

**Scale-Out Fabric:** Specialized form of a network, with a fully-connected topology, that is engineered and tuned to sustain performance & latency at high scale while reducing jitter (e.g., Cloud Ethernet and HPC Fabric)

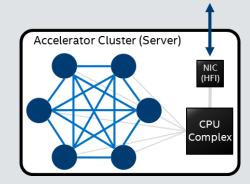

#### DATA AND THE EMERGENCE OF ACCELERATOR NETWORKS

#### Node-focused:

- Light-weight network that interconnects a cluster of local accelerators with highbandwidth, low-latency links

- Lowest power/bit

- •Code & connectivity optimized for locality

- Emerging Need: Data-lakes

#### Accelerator scaling fabric:

Used for high-bandwidth memory sharing/coordination at larger scale

Allows separation of accelerator vs. general communications, minimizing interference in the scaling fabric.

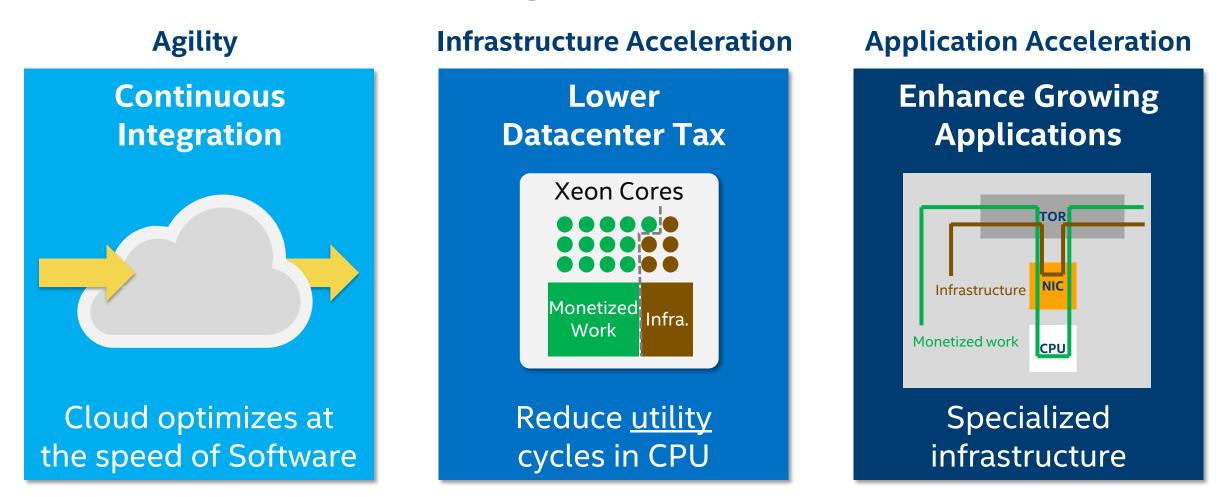

## The motivation driving acceleration and offload

Objective: Grow acceleration capabilities for network-related workloads

## Emerging use case : bare-metal server

#### Bare metal servers

- Offer new usage models—full server rentals

- Improve infrastructure security in cloud

- Bolster performance, reduce cost/bit by removing bottlenecks

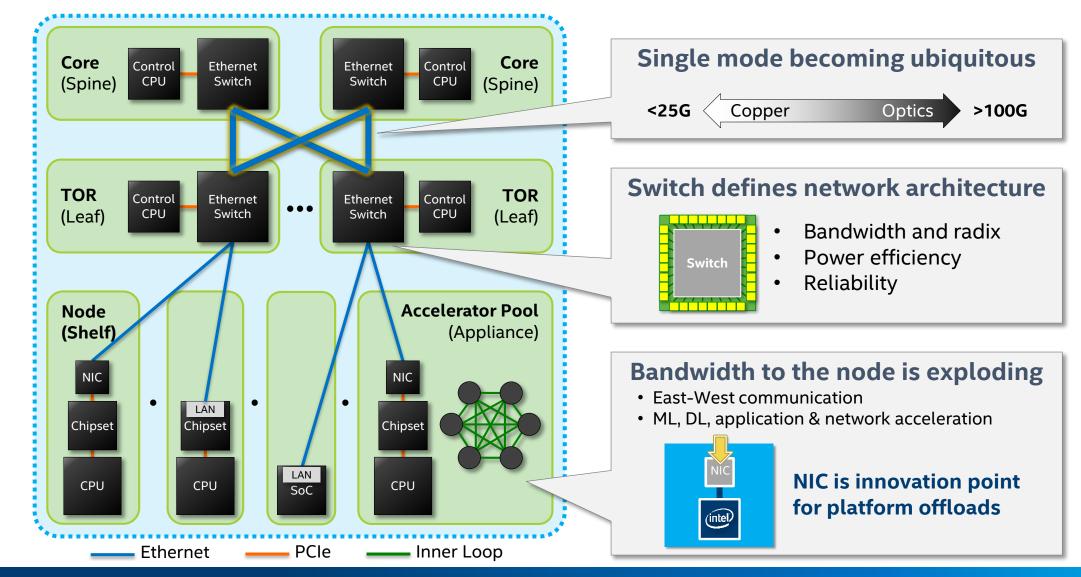

## Cloud-era data center network

Pod .....

intel

8

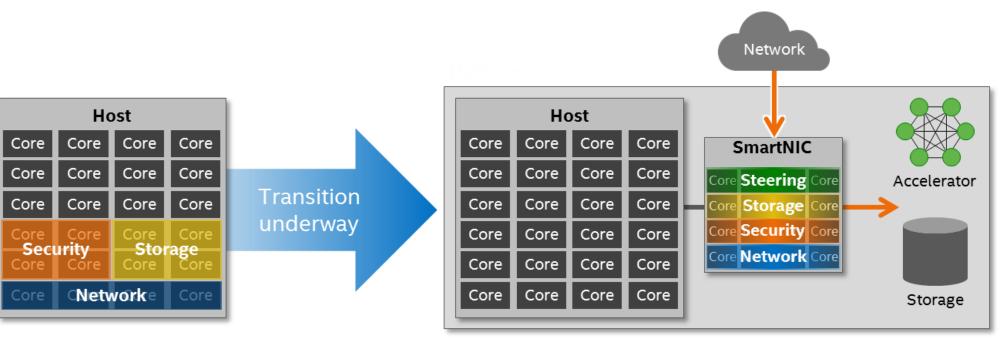

## Motivating smart NIC

#### Integrating end-to-end capabilities in the platform

| CORES/COMPUTE                                                                                                                                                         | FPGA                                                                                                                                                   | <b>HOST INTERFACES</b>                                                                                                         | INTERFACE TECH.                                                                                                       | Programmable assets                                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| <ul> <li>Xeon/Core</li> <li>Atom</li> <li>Graphics/Media</li> <li>QAT/Crypto/Comp.</li> <li>Special purpose<br/>(accelerators)</li> </ul>                             | <ul> <li>Arria10</li> <li>Stratix10</li> <li>Flexible tile<br/>architecture</li> </ul>                                                                 | <ul> <li>PCIe Gen3, 4 and 5</li> <li>IAL (I/0, Memory,<br/>Cache)</li> <li>UPI/Coherent</li> <li>On-package (Rlink)</li> </ul> | <ul> <li>DMA</li> <li>SVM/Coherent</li> <li>Hardware queue<br/>engines</li> <li>Virtual device<br/>manager</li> </ul> | <ul> <li>FPGA</li> <li>CPUs</li> <li>Flexible state machines</li> </ul>                       |  |

| NETWORK                                                                                                                                                               | SOFTWARE                                                                                                                                               | PACKAGE                                                                                                                        | <b>STORAGE MEMORY</b>                                                                                                 | <ul> <li>Networking assets</li> <li>Broad market NIC</li> </ul>                               |  |

| <ul> <li>MAC/PHY/SerDes</li> <li>RDMA (RoCE, iWARP)</li> <li>OPA for HPC</li> <li>Packer parsers</li> <li>P4 engines</li> <li>Schedulers</li> <li>Switches</li> </ul> | <ul> <li>Compilers, tools</li> <li>WOS</li> <li>OTC/Intel Clear Linux</li> <li>P4 API working group</li> <li>Libraries/Standards<br/>bodies</li> </ul> | <ul> <li>BGA: Low-cost to<br/>large footprint</li> <li>Package MCP &amp;<br/>Interfaces (Rlink)</li> </ul>                     | • NVMe                                                                                                                | <ul> <li>Broad market NIC<br/>business</li> <li>Open source contribs</li> <li>DPDK</li> </ul> |  |

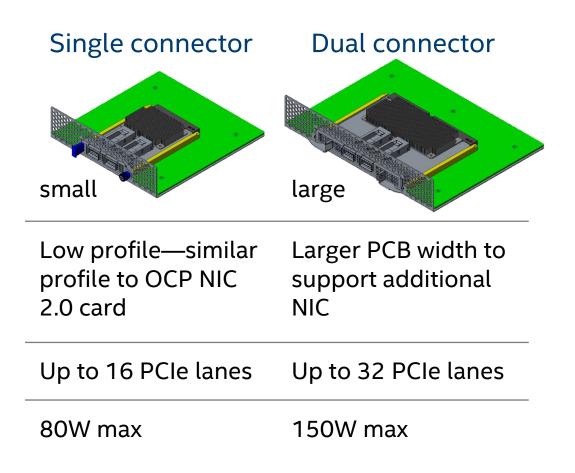

## OCP NIC v3.0 enables the smart NIC

Joint effort across system/NIC/Connector suppliers and end users

Community development since Feb 2017 solved major challenges

- Improved serviceability

- Manage NIC / platform transition

- Ready for PCIe Gen4 and Gen5

- Enlarge PCB space for smart NIC use case

- Allow higher TDP ASICs

- Improve mechanical interface

## Significant OCP contributions in...

#### **OCP Ethernet Network Adapters**

>25 OCP-compliant NIC and PHY SKUs, covering 1GbE, 10GbE, 25GbE, and 40GbE

>1M Intel-branded ports shipped in OCP form factor (excluding partner shipments)

#### **100G Silicon Photonics**

Fully compliant with 100G CWDM4-OCP, CWDM4 MSA, QSFP, and CAUI-4 specs

500m, 2km, or 10km reach on duplex single mode fiber

## Intel 400G CWDM8 QSFP-DD optical module

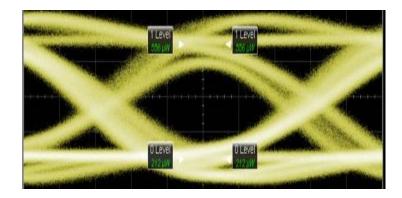

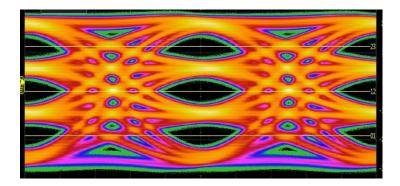

Technology for 400G is working in the lab

| 1271<br>nm          | 1291<br>nm            | 1311<br>nm             | 1331<br>nm   | 1351<br>nm                                                                                                       | 1371<br>nm                                                                                                      | 1391<br>nm     | 1411<br>nm      |

|---------------------|-----------------------|------------------------|--------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|-----------------|

|                     |                       |                        |              |                                                                                                                  |                                                                                                                 |                |                 |

|                     |                       |                        |              |                                                                                                                  |                                                                                                                 |                |                 |

|                     |                       |                        |              |                                                                                                                  |                                                                                                                 |                |                 |

|                     |                       |                        |              |                                                                                                                  |                                                                                                                 |                |                 |

|                     |                       |                        |              |                                                                                                                  |                                                                                                                 |                |                 |

| ····                |                       | ·····                  |              |                                                                                                                  |                                                                                                                 |                |                 |

| a Maria Maria Maria | din <mark>bili</mark> | Addison and the second | thainte hand | thread a state of the | and the state of the | Install street | n fan te fan te |

**400G Transmitter: Optical Output**

#### **400G Receiver: Host Side Electrical Output**

# **DCP** SUMMT